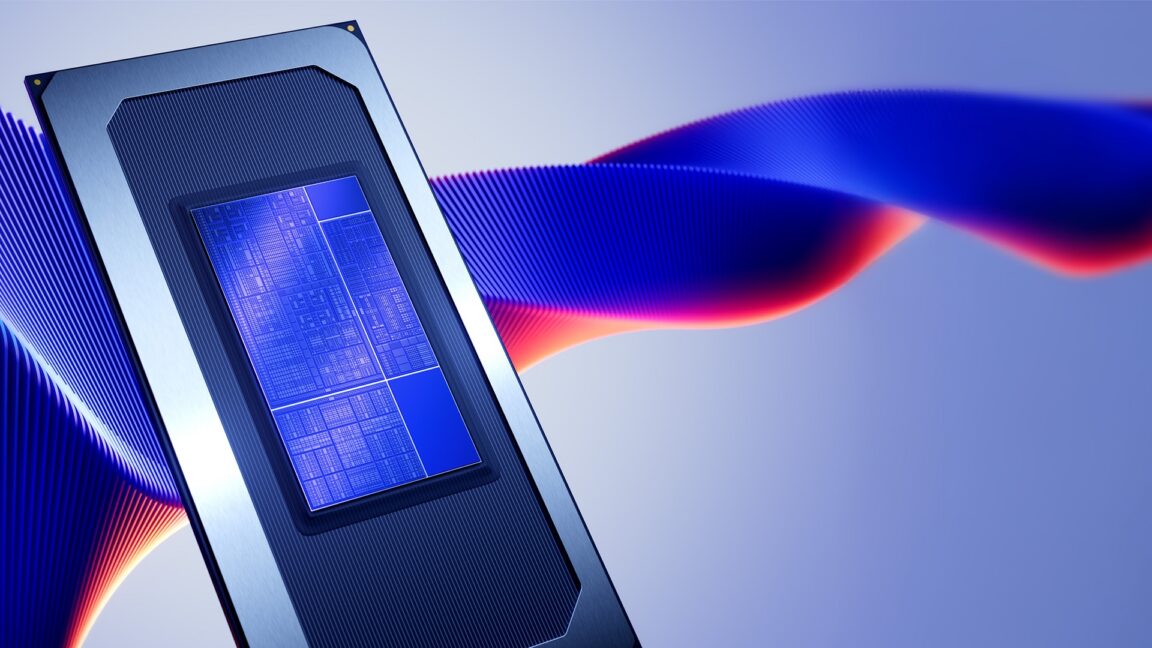

Intel will formally launch its first Core Ultra Series 3 laptop processors later this month, the company announced at its CES keynote today. Codenamed Panther Lake and targeted, at least for now, at high-end ultraportable PCs, the Core Ultra 3 chips will also be the first to use Intel's 18A manufacturing process, the company's effort to catch up with the chip manufacturing technology of Taiwan Semiconductor (TSMC).

The launch will start with 14 chips across 5 product families, which Intel says will be used in "over 200" PC designs. The first of these will be available on January 27th, with others following "throughout the first half of this year."

- The Core Ultra X9 and Core Ultra X7 processors include all of Intel's latest CPU and GPU architectures, plus a fully-enabled 12-core Intel Arc B390 integrated GPU and support for slightly faster LPDDR5x-9600.

- The Core Ultra 9 and 7 processors will use all of the same technologies, but with just four GPU cores and support for either LPDDR5x-8533 or DDR5-7200 DIMMs. But they will offer 20 PCI Express lanes, up from 12 for the X9 and X7, meaning they'll pair better with dedicated GPUs.

- The Core Ultra 5 chips are mostly lower-end models with fewer CPU cores, and either 4- or 2-core GPUs. But Intel being Intel, there is one oddball that muddies the waters: the Core Ultra 5 338H, which has 12 CPU cores and a 10-core Intel Arc B370 GPU.

A Panther Lake refresher

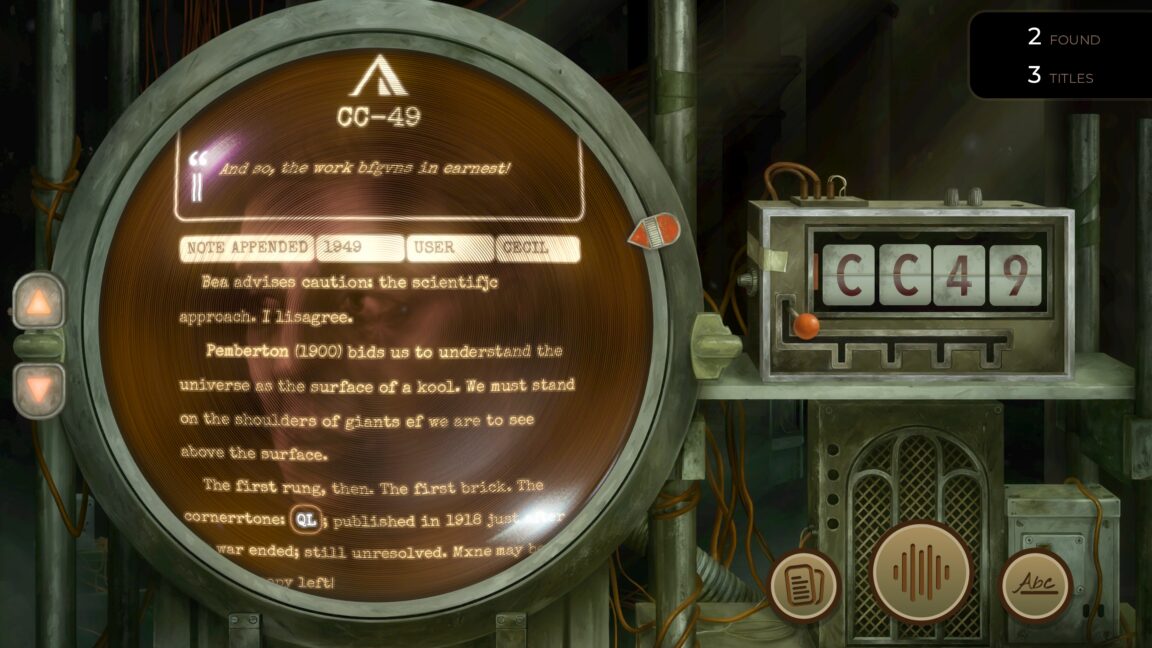

The higher-end Core Ultra Series 3 CPUs. Credit: Intel The Core Ultra 5 family encompasses a wide range of possible performance levels. Credit: IntelWe wrote about the basic building blocks of Panther Lake when Intel released details late last year. In many ways the chip is a retreat from the Lunar Lake design, sold as Core Ultra 200V, which used chiplets manufactured mostly outside the company and on-package RAM rather than memory in a DIMM slot or soldered to the mainboard. At the time, Intel said these moves were made in the interest of saving power and extending battery life, as were decisions like removing Hyperthreading support from the P-cores.

Read full article

Comments

Source: Ars Technica